导读:与芯片制造相关的最大营销术语之一是特征尺寸。到底是10、7还是5?让我们进入制程节点的世界一探究竟。

图片来自“123rf.com.cn”

在计算机芯片领域,往往数字越大越好。更多内核,更高GHz,更快的浮点运算,工程师和用户都希望这样。但现在有一个衡量标准火了,越小越好。它究竟是什么?为什么会这么重要?为什么以纳米为单位测量?为什么我们要走进芝麻街,把这篇文章带到你面前,数字到底是10、7还是5?让我们进入制程节点的世界一探究竟。

在深入研究之前,值得花些时间研究一下CPU架构。在第一部分中,我们介绍了处理器的基本架构,在第二部分中,我们研究了工程师如何规划和设计它们。

与本文相关的关键部分是解释如何将计算机芯片物理地组合在一起。如果您想深入了解制造工艺,您需要仔细阅读光刻部分,而在本章节中,我们将重点介绍以下几点:

与芯片制造相关的最大营销术语之一是特征尺寸。

在芯片工业中,特征尺寸与被称为制程节点的东西有关。正如我们在第3部分“CPU的设计”中提到的,这是一个相当宽松的术语,因为不同的制造商使用这个短语来描述芯片本身的不同方面,但不久前它被用来描述晶体管两个部分之间最小的间隙。

今天,它更像是一个营销术语,对于比较生产方法不太有用。也就是说,晶体管是处理器的一个关键特性,由于它们的组执行所有的数字处理和数据存储都在芯片内,因此非常需要来自同一制造商的更小的制程节点。显而易见,你想问为什么?

在处理器的世界里,什么都不会立即发生,也不会在不需要电源的情况下发生。更大的元件需要更长的时间来改变它们的状态,信号需要更长的时间来传输,并且需要更多的能量来移动处理器的电子。虽然听起来不笨重,但更大的元器件占用更多的物理空间,因此芯片本身更大。

在上图中,我们看到的是三个旧的Intel CPU。从左边开始,分别是2006年的赛扬,2004年的奔腾M以及1995年的旧奔腾。它们的制程节点分别为65、90和350纳米。换言之,24年来设计中的关键部件比13年来设计中的关键部件大5倍以上。另一个重要的区别是,新的芯片内置了大约2.9亿个晶体管,而原来的奔腾只有300多万个,几乎是几百倍的差距。

虽然制程节点的减少只是最近设计的物理尺寸更小、晶体管数量更多的原因之一,但它确实在英特尔能够提供这一功能方面发挥了重要作用。

真正的问题是:与奔腾的12W相比,赛扬产生了大约30W的热量。这种热量来自这样一个事实:当电流(electricity)被推到芯片的电路上时,能量通过不同的过程而损失,绝大多数能量以热量的形式释放出来。是的,30是一个比12大的数字,但别忘了,赛扬芯片上的晶体管比奔腾多近100倍。

因此,如果拥有一个更小的制程节点的好处会是产生更小的芯片,能使更多的晶体管可以更快地转换,实现更强的计算,以及减少能量作为热量的损失。那么为题来了——为什么不是每一个芯片都使用尽可能最小的制程节点呢?

这就要从另一个方向谈起——要有光!

At this point, we need to have a look a process called photolithography: light is passed through something called 在这一点上,我们需要看一个称为光刻的过程:光通过一种称为光掩模的东西,这个东西在某些区域阻挡光,并让其通过其他区域。在经过的地方,光线会聚焦成一个小点,然后它会与芯片制造过程中使用的特殊层反应,帮助确定各个部件的位置。

想象一下,这就像是你手上的X光:骨头阻挡了光线,充当光掩模,而肉体让它通过,产生了手的内部结构的图像。

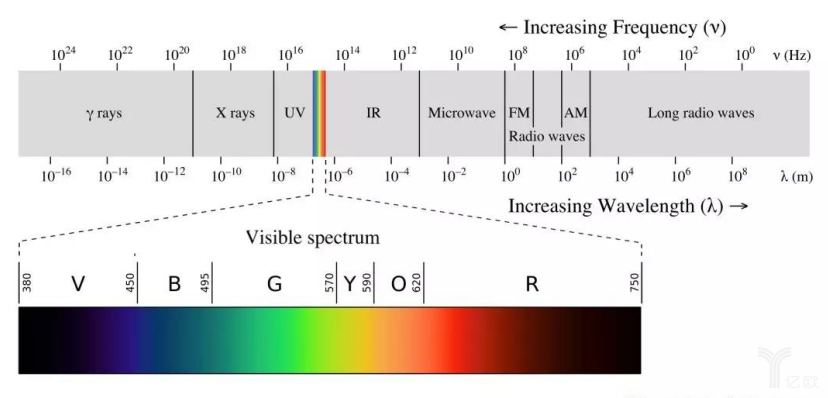

光实际上并没有被使用——即使是像旧奔腾这样的芯片,它也太大了。你可能很想知道为什么光会有大小的说法,实际上它与波长有关。光是一种叫做电磁波的东西,是一种不断循环的电场和磁场混合物。

虽然我们使用经典的正弦波来观察形状,但电磁波并没有真正的形状。更重要的是,当它们与某种事物发生交互时,它们产生的效果遵循这种模式。这种循环模式的波长是两个相同点之间的物理距离:想象海浪在沙滩上滚动,波长是海浪顶部的距离。电磁波的波长范围很广,因此我们将它们放在一起并将其称为光谱。

小,小,最小

在下面的图片中,我们可以看到我们所说的光只是这个光谱中的一小部分。还有其他熟悉的名字:无线电波、微波、X射线等等。我们还可以看到波长的一些数字;光的大小大约是10-7米,或者大约是0.000004英寸!

科学家和工程师更喜欢用一种稍有不同的方法来描述这么小的长度,即纳米或nm。如果我们观察光谱的扩展部分,我们可以看到光实际上在380纳米到750纳米之间。

图片来源:Philip Ronan,Gringer

回顾一下这篇文章,重新阅读关于旧赛扬芯片的部分 - 它是在65纳米制程节点上制造的。那么,怎样才能制造出比光小的零件呢?简单:光刻工艺没有使用光,而是使用紫外线(亦称UV)。

在光谱图中,UV从大约380 nm开始(光消失时)并一直缩小到大约10 nm。英特尔,台积电和GlobalFoundries等制造商使用一种称为EUV(极紫外线)的电磁波,大小约为190nm。这种微小的波动不仅意味着组件本身可以被制造得更小,而且它们的整体质量可能更好。这使得不同的部件可以紧密地封装在一起,有助于缩小芯片的总体尺寸。

不同的公司为其使用的流程节点的规模提供不同的名称。英特尔将他们最新的一款产品命名为p1274或“10nm”,而台积电则简单地称之为“10FF”。AMD等处理器设计师为较小的制程节点创建布局( layout )和结构(structures),然后依靠台积电这样的公司来生产它们,后者在今年早些时候加快了他们的“7nm”产险的扩产步伐。在这种生产规模下,一些最小的特征点只有6纳米宽(不过,大多数功能都比这大得多)。

为了真正了解6纳米有多小,我们这样看。构成处理器主体的硅原子间距大约为0.5纳米,原子本身的直径大约为0.1纳米。因此,作为一个大概的数字,台积电的工厂处理的晶体管覆盖宽度小于10个硅原子。

瞄准原子的挑战

撇开芯片制造商正在努力开发只有少数几个原子宽的特征点这一令人难以置信的事实不谈,EUV光刻技术已经引发了一系列严重的工程和制造问题。

英特尔一直在努力使其10纳米的产量达到14纳米的水平;去年,GlobalFoundries停止了7nm和更小的生产系统的所有开发进程。虽然英特尔和GF的问题可能不是由于EUV光刻固有的困难造成的,但不能说完全无关。

电磁波的波长越短,其承载的能量越多,这导致对制造的芯片的损坏的可能性更大; 非常小规模的制造对正在使用的材料中的污染和缺陷也非常敏感。其他问题,如衍射极限(diffraction limits )和统计噪声( statistical noise :EUV波传输的能量沉积到芯片层的自然变化),也与实现100%完美芯片的目标相悖。

还有一个问题是,在原子这个奇怪的世界里,电流和能量转移不能再假定为遵循经典的系统和规则。以运动的电子(构成原子的三个粒子之一)的形式保持电能沿着导体向下流动,在我们习惯的尺度上相对容易——只要用一层厚厚的绝缘层包裹导体。

从过年英特尔和台积电的工作现状看,这变得更难实现,因为绝缘层还不够厚。不过,目前生产问题几乎都与EUV光刻技术固有的问题有关,因此,我们还需要几年的时间才能开始在论坛上讨论Nvidia比AMD更好地处理量子行为或其他类似的胡说八道!

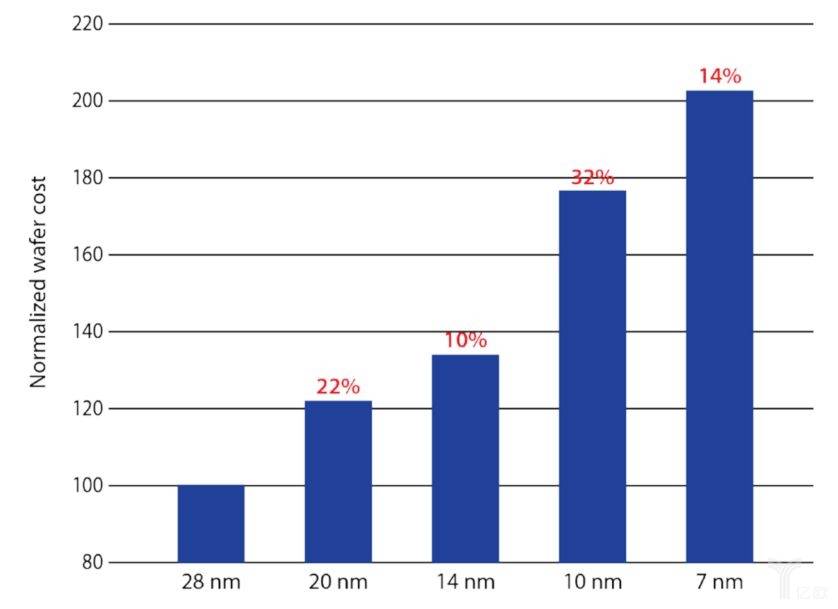

这是因为真正的问题,即生产困难背后的最终原因,是英特尔,台积电及其所有制造伙伴都是纯粹的商业企业,他们将原子用于创造未来收入作为唯一目的。但在Mentor的商业研究报告中,提供了以下概述,越小的制程节点就需要越高的晶圆成本。

例如,如果我们假设28纳米进程节点与英特尔用于生产其Haswell系列CPU的节点相同(如酷睿i7-4790K),那么他们的10纳米系统的每片晶圆成本几乎是前者的两倍。每片晶圆能够生产的芯片数量在很大程度上取决于每片芯片的大小,但采用较小的工艺规模意味着一片晶圆可能会产生更多的芯片来销售,这有助于抵消成本的增加。最终,尽可能多的成本将通过提高产品零售价格推向消费者,但这必须与行业需求相平衡。

过去几年智能手机销量的增长,以及家庭和汽车智能技术的近乎指数级增长,意味着芯片制造商不得不承受因为进入较小的制程节点而遭受的财务损失,直到整个系统足够成熟,能够生产出高产量的晶圆(即那些含有尽可能少的缺陷的晶圆)。鉴于我们谈论的是一项数十亿美元的风险很大的业务,这也是GlobalFoundries退出先进制程竞赛的原因之一。

前景

如果这一切听起来有些悲观,但我们不应该否认,眼前的未来看起来是积极的。三星和台积电的7nm生产线不仅在数量和收入方面上实现了良好运营,而且芯片设计者也在计划在其产品中使用多个节点。近来最著名的例子是AMD最近宣布的Ryzen 3900X CPU的芯片设计。

这款顶级台式PC处理器将采用台积电7纳米节点来制造两款芯片,以及由GlobalFoundries制造的一款14纳米芯片。前者将是实际的处理器部件,而后者将处理连接到CPU的DDR4内存和PCI Express设备。假设这种设计按预期工作(并且没有理由怀疑它应该如此),那么我们几乎肯定会看到更多的公司遵循这个多节点设置。

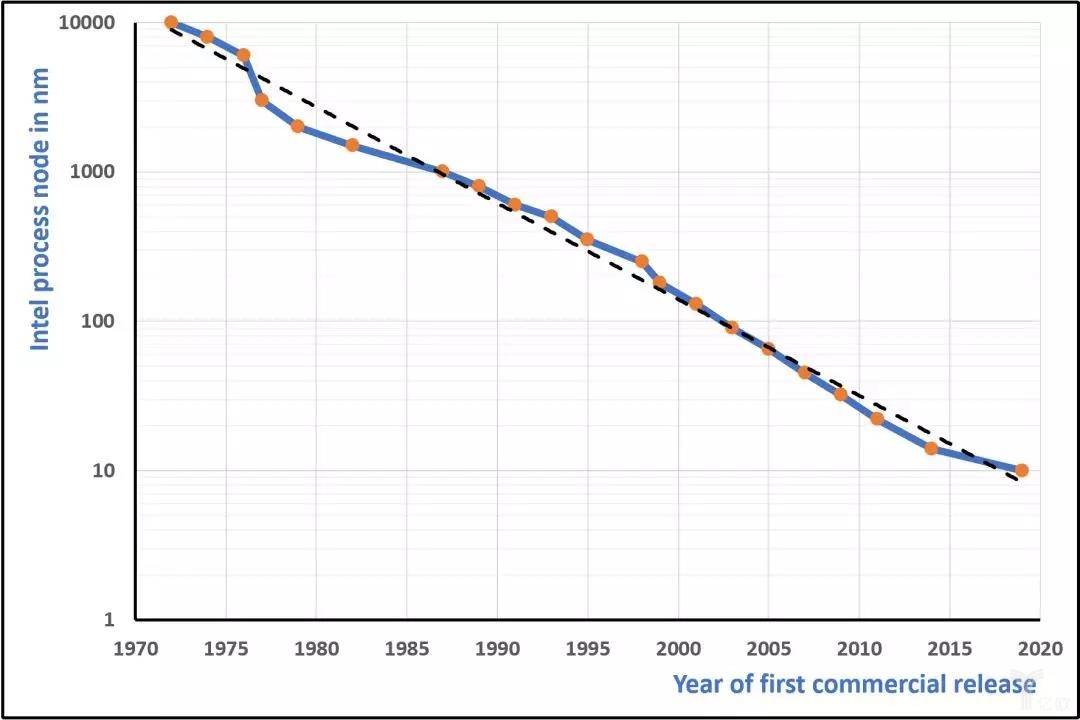

上图显示了英特尔制程节点在过去50年中的变化。垂直轴以10倍的系数显示节点大小,从10000 nm开始一直向上。该芯片巨头已经遵循了4.5年的粗略节点半衰期(每次减少一半节点大小所花费的时间)。

那么,这是否意味着到2025年我们将看到5纳米的英特尔?可能是的,尽管他们最近在10纳米的技术上遇到了困难。但三星和台积电一直在推进他们的5纳米研究,因此未来对各种处理器都是有利的。

它们将越来越小,速度越来越快,能耗越来越低,性能也越来越高。它们将引领人们走向全自动汽车,具有当前智能手机的电量和电池寿命的智能手表,以及超过十年前数百万美元电影中所见的游戏中的图形。